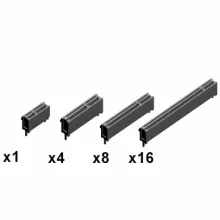

PCI Express (PCIe) is a high-speed serial expansion bus standard designed to replace legacy PCI, PCI-X, and AGP interfaces. Unlike older shared parallel buses, PCIe uses a point-to-point architecture with dedicated lanes, enabling full-duplex communication, higher bandwidth, and better scalability. Each link can use one or multiple lanes (×1 to ×16), with bandwidth scaling accordingly. PCIe also introduces advanced features such as improved error reporting, hot-plug support, and hardware virtualization. Maintained by the PCI-SIG, PCIe is widely used in modern PCs, servers, storage, and expansion cards, delivering reliable performance for graphics, networking, and high-speed I/O devices.